# IBM Power E1080 Technical Overview and Introduction

Tim Simon

Dean Mussari

**Tsvetomir Spasov**

**Power Systems**

**IBM Redbooks**

#### **IBM Power E1080 Technical Overview and Introduction**

November 2024

| <b>Note:</b> Before using this information and the product it supports, read the information in "Notices" on page vii. |

|------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

| Construct Edition (November 2004)                                                                                      |

| Second Edition (November 2024)  This edition applies to IBM Power E1080 - 9080-HEX.                                    |

© Copyright International Business Machines Corporation 2021, 2024. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

# **Contents**

| Notices                                             |        |

|-----------------------------------------------------|--------|

| Preface                                             | ix     |

| Authors                                             |        |

| Now you can become a published author, too!         |        |

| Comments welcome                                    |        |

| Stay connected to IBM Redbooks                      |        |

| Summary of changes                                  | viii   |

| November 2024, Second Edition                       |        |

| November 2024, Jecona Lattori                       | . AIII |

| Chapter 1. Introducing IBM Power E1080              | 1      |

| 1.1 System overview                                 |        |

| 1.1.1 System nodes, processors, and memory          | 2      |

| 1.1.2 Expansion drawers and storage enclosures      |        |

| 1.1.3 Hardware at-a-glance                          |        |

| 1.1.4 System capacities and features                |        |

| 1.2 System nodes                                    |        |

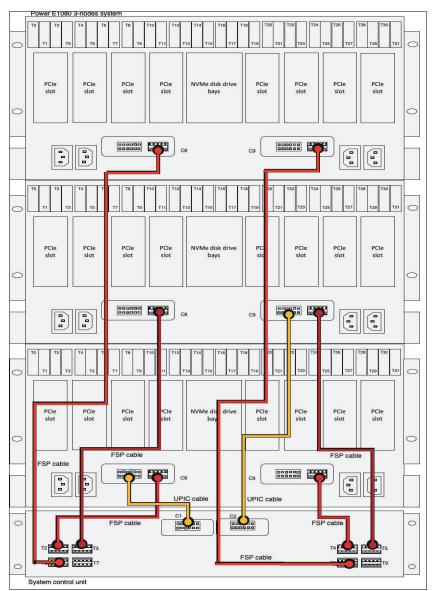

| 1.3 System control unit                             |        |

| 1.4 Server specifications                           |        |

| 1.4.1 Physical dimensions                           |        |

| 1.4.2 Electrical characteristics                    |        |

| 1.4.3 Environment requirements and noise emission   |        |

| 1.5 System features                                 |        |

| 1.5.1 Minimum configuration                         |        |

| 1.5.2 Processor features                            |        |

| 1.5.3 Memory features                               |        |

| 1.5.4 System node PCIe features                     |        |

| 1.5.5 System node disk and media features           |        |

| 1.5.6 System node USB features                      |        |

| 1.5.7 Power supply features                         |        |

| 1.6 I/O drawers                                     |        |

| 1.6.1 System node PCIe interconnect features        |        |

| 1.6.2 I/O expansion drawers                         |        |

| 1.6.3 Disk expansion drawers                        |        |

| 1.6.4 IBM System Storage                            |        |

| 1.7 System racks                                    |        |

| 1.7.1 New rack considerations                       |        |

| 1.7.2 IBM Enterprise 42U Slim Rack 7965-S42         |        |

| 1.7.3 AC power distribution unit and rack content   | . 31   |

| 1.7.4 PDU connection limits                         |        |

|                                                     |        |

| 1.7.5 Rack-mounting rules                           |        |

| 1.7.6 Useful rack additions                         |        |

| 1.7.7 Original equipment manufacturer racks         |        |

| 1.8 Hardware Management Console overview            |        |

| 1.8.1 HMC 7063-CR2                                  |        |

| 1.8.2 Virtual HMC                                   |        |

| Lo.3 DIVID RELIWORK CONNECTIVITY (UIES TOT /Ub3-CH2 | . 41   |

| 1.8.4 High availability HMC configuration                               |      |

|-------------------------------------------------------------------------|------|

| 1.8.5 HMC code level requirements for the Power E1080                   |      |

| 1.8.6 HMC currency                                                      | 44   |

| Chapter 2. Architecture and technical overview                          | 45   |

| 2.1 IBM Power10 processor                                               |      |

| 2.1.1 Power10 processor overview                                        |      |

| 2.1.2 Power10 processor core                                            |      |

| 2.1.3 Simultaneous multithreading                                       |      |

| 2.1.4 Matrix Math Accelerator Al workload acceleration                  |      |

| 2.1.5 Power10 compatibility modes                                       |      |

| 2.1.6 Processor Feature Codes                                           |      |

| 2.1.7 On-chip L3 cache and intelligent caching                          |      |

| 2.1.8 Open memory interface                                             |      |

| 2.1.9 Pervasive memory encryption                                       |      |

| 2.1.10 Nest accelerator                                                 |      |

| 2.1.11 SMP interconnect and accelerator interface                       |      |

| 2.1.12 Power and performance management                                 |      |

| 2.1.13 Comparing Power10, Power9, and Power8 processors                 |      |

| 2.2 SMP interconnection                                                 |      |

| 2.2.1 Two-system node drawers OP-bus connection                         |      |

| 2.2.2 SMP cable reliability, availability, and serviceability attribute |      |

| 2.3 Memory subsystem                                                    |      |

| 2.3.1 Memory bandwidth                                                  |      |

| 2.3.2 Memory placement rules                                            |      |

| 2.4 Capacity on Demand                                                  |      |

| 2.4.1 New CoD features                                                  |      |

| 2.4.2 IBM Power Private Cloud with Shared Utility Capacity              |      |

| 2.4.3 Static, Mobile, and Base activations                              |      |

| 2.4.4 Capacity Upgrade on Demand                                        |      |

| 2.4.5 Elastic CoD (Temporary)                                           |      |

| 2.4.6 IBM Power Enterprise Pools 1.0 and Mobile CoD                     |      |

| 2.4.7 Utility CoD                                                       |      |

| 2.4.8 Trial CoD                                                         |      |

| 2.4.9 Software licensing and CoD                                        |      |

| 2.5 Internal I/O subsystem                                              |      |

| 2.5.1 Internal PCIe Gen 5 subsystem and slot properties                 |      |

| 2.5.2 Internal NVMe storage subsystem                                   |      |

| 2.5.3 USB subsystem                                                     |      |

| 2.5.4 PCle slots features                                               |      |

| 2.6 Supported PCIe adapters                                             |      |

| 2.6.1 LAN adapters                                                      |      |

| 2.6.2 Fibre Channel adapters                                            |      |

| 2.6.3 SAS adapters                                                      |      |

| 2.6.4 Crypto adapter                                                    |      |

| 2.6.5 USB adapter                                                       |      |

| 2.6.6 I/O expansion drawers                                             |      |

| 2.6.7 Disk drawer                                                       |      |

| 2.6.8 SFP transceiver                                                   |      |

|                                                                         |      |

| 2.7 External I/O subsystems                                             |      |

| 2.7.1 Pole Gena I/O expansion drawer                                    |      |

| 2.7.2 Pole Gens I/O Expansion Drawer                                    |      |

|                                                                         | 1110 |

| 2.8.1 NED24 NVMe Expansion Drawer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 106                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 2.8.2 IBM EXP24SX SAS Storage Enclosure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| 2.9 System control and clock distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| 2.10 Operating system support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 2.10.1 Power E1080 prerequisites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

| 2.10.2 AIX operating system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| 2.10.3 IBM i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| 2.10.4 Linux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| 2.10.5 Virtual I/O Server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| 2.10.6 Entitled System Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

| 2.10.7 Update Access Keys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| 2.11 Manageability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 127                                                                                     |

| 2.11.1 Service user interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 127                                                                                     |

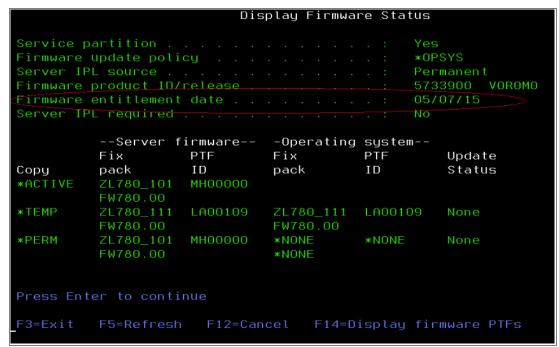

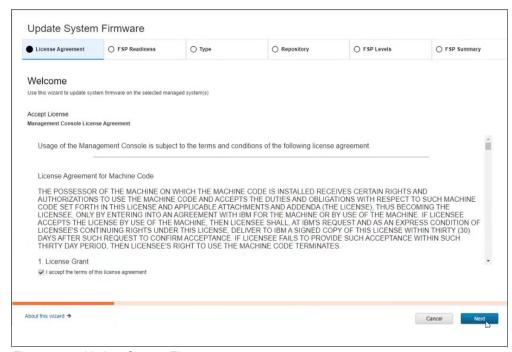

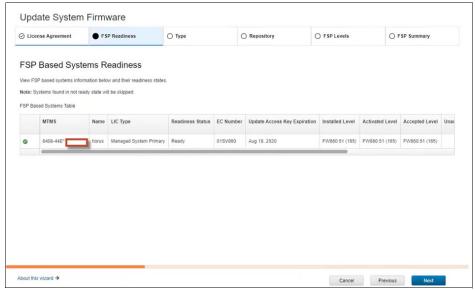

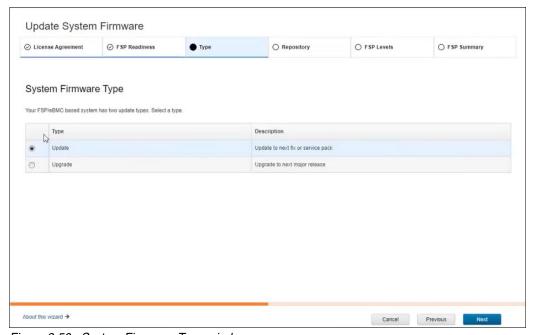

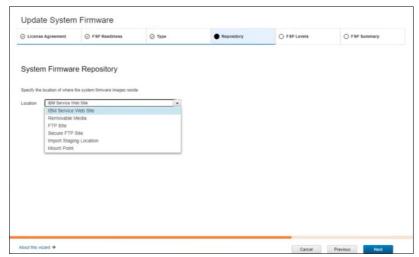

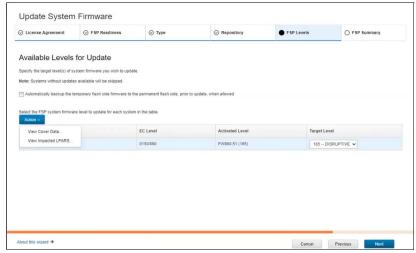

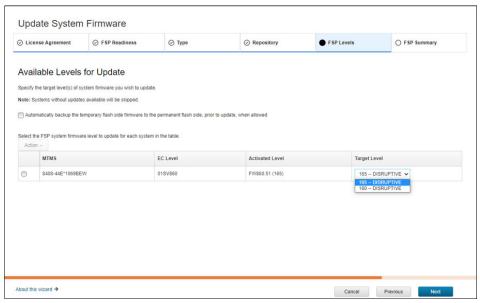

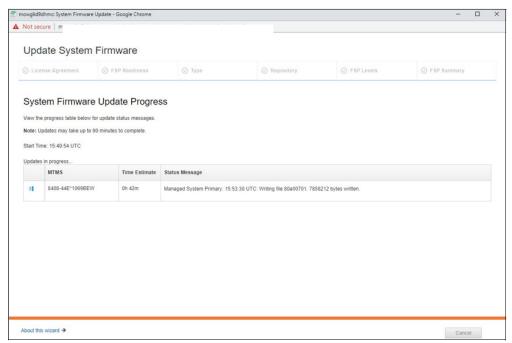

| 2.11.2 System firmware maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 128                                                                                     |

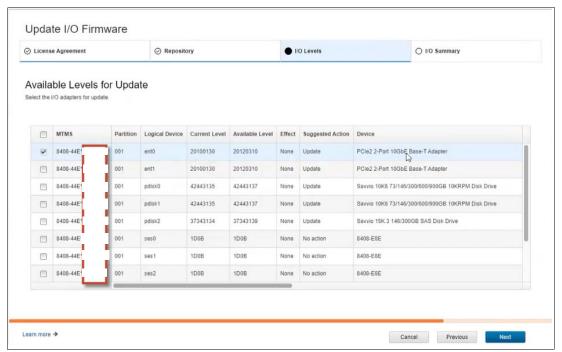

| 2.11.3 I/O firmware update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 132                                                                                     |

| 2.12 Serviceability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

| 2.12.1 Error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

| 2.12.2 Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 2.12.3 Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

| 2.12.4 Notification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

| 2.12.5 Ease of location and service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

| 2.12.5 Lase of location and service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                                                                                     |

| Chapter 3. Enterprise solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 139                                                                                     |

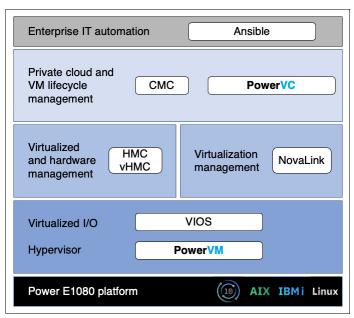

| 3.1 PowerVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| 3.1.1 IBM POWER Hypervisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

| 3.1.2 Multiple shared processor pools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

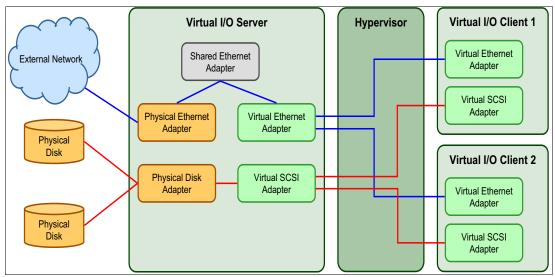

| 3.1.3 Virtual I/O Server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

| 3.1.4 Live Partition Mobility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 3.1.5 Active Memory Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

| 3.1.6 Remote Restart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| 3.1.7 POWER processor modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

| 3.1.8 Single Root I/O Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 3.1.9 More information about virtualization features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 149                                                                                     |

| 3.2 IBM PowerVC overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149<br>149                                                                              |

| 3.2 IBM PowerVC overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149<br>149<br>149                                                                       |

| 3.2 IBM PowerVC overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149<br>149<br>149<br>150                                                                |

| 3.2 IBM PowerVC overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149<br>149<br>149<br>150                                                                |

| 3.2 IBM PowerVC overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149<br>149<br>149<br>150<br>152                                                         |

| 3.2 IBM PowerVC overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149<br>149<br>149<br>150<br>152<br>152                                                  |

| 3.2 IBM PowerVC overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149<br>149<br>149<br>150<br>152<br>152<br>152                                           |

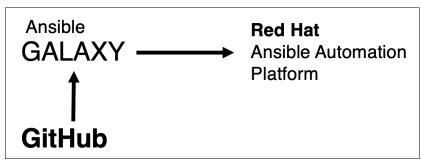

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX                                                                                                                                                                                                                                                                                                                                                                                            | 149<br>149<br>150<br>152<br>152<br>152<br>153                                           |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i                                                                                                                                                                                                                                                                                                                                                           | 149<br>149<br>150<br>152<br>152<br>152<br>153<br>153                                    |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS.                                                                                                                                                                                                                                                                                             | 149<br>149<br>150<br>152<br>152<br>152<br>153<br>153                                    |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS. 3.4 Protect trust from core to cloud.                                                                                                                                                                                                                                                       | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153                                    |

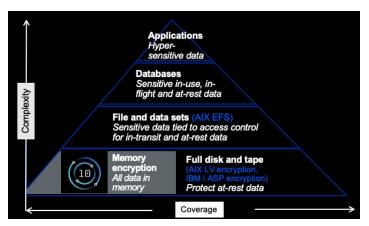

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption                                                                                                                                                                                                  | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>153                             |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS. 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption 3.4.2 Quantum-safe cryptography support.                                                                                                                                                        | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>154<br>155                      |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS. 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption 3.4.2 Quantum-safe cryptography support. 3.4.3 IBM PowerSC support                                                                                                                              | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>153<br>154<br>155<br>155        |

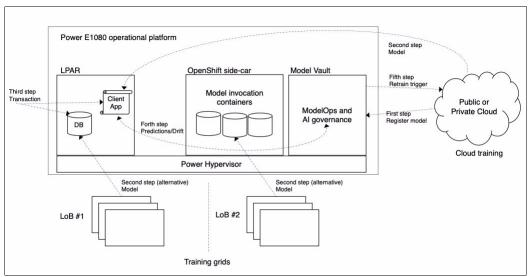

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS. 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption 3.4.2 Quantum-safe cryptography support 3.4.3 IBM PowerSC support 3.5 Running artificial intelligence where operational data is stored.                                                         | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>154<br>155<br>155               |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS. 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption 3.4.2 Quantum-safe cryptography support. 3.4.3 IBM PowerSC support                                                                                                                              | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>154<br>155<br>155               |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS. 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption 3.4.2 Quantum-safe cryptography support. 3.4.3 IBM PowerSC support 3.5 Running artificial intelligence where operational data is stored. 3.5.1 Training anywhere, and deploying on Power E1080. | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>153<br>154<br>155<br>156<br>157 |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for VIOS 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption 3.4.2 Quantum-safe cryptography support 3.4.3 IBM PowerSC support 3.5 Running artificial intelligence where operational data is stored. 3.5.1 Training anywhere, and deploying on Power E1080.                                 | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>154<br>155<br>156<br>157        |

| 3.2 IBM PowerVC overview 3.2.1 IBM PowerVC functions and advantages 3.3 System automation with Ansible 3.3.1 Ansible Automation Platform. 3.3.2 Power servers in the Ansible ecosystem 3.3.3 Ansible modules for AIX 3.3.4 Ansible modules for IBM i 3.3.5 Ansible modules for HMC 3.3.6 Ansible modules for VIOS. 3.4 Protect trust from core to cloud 3.4.1 Crypto engines and transparent memory encryption 3.4.2 Quantum-safe cryptography support. 3.4.3 IBM PowerSC support 3.5 Running artificial intelligence where operational data is stored. 3.5.1 Training anywhere, and deploying on Power E1080. | 149<br>149<br>150<br>152<br>152<br>153<br>153<br>153<br>154<br>155<br>155<br>156<br>157 |

| <b>Abbreviations</b> | and acronyms | <br>61 |

|----------------------|--------------|--------|

|                      |              |        |

# **Notices**

This information was developed for products and services offered in the US. This material might be available from IBM in other languages. However, you may be required to own a copy of the product or product version in that language in order to access it.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not grant you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive, MD-NC119, Armonk, NY 10504-1785, US

INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some jurisdictions do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM websites are provided for convenience only and do not in any manner serve as an endorsement of those websites. The materials at those websites are not part of the materials for this IBM product and use of those websites is at your own risk.

IBM may use or distribute any of the information you provide in any way it believes appropriate without incurring any obligation to you.

The performance data and client examples cited are presented for illustrative purposes only. Actual performance results may vary depending on specific configurations and operating conditions.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

Statements regarding IBM's future direction or intent are subject to change or withdrawal without notice, and represent goals and objectives only.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to actual people or business enterprises is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrate programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. The sample programs are provided "AS IS", without warranty of any kind. IBM shall not be liable for any damages arising out of your use of the sample programs.

#### **Trademarks**

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corporation, registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the web at "Copyright and trademark information" at https://www.ibm.com/legal/copytrade.shtml

The following terms are trademarks or registered trademarks of International Business Machines Corporation, and might also be trademarks or registered trademarks in other countries.

AIX® IBM FlashSystem® Power8®

Db2® IBM Spectrum® Power9®

Easy Tier® IBM Z® PowerVM®

IBM® Micro-Partitioning® Redbooks®

IBM Cloud® POWER® Redbooks (logo) ® ®

IBM FlashCore® Power Architecture®

The following terms are trademarks of other companies:

The registered trademark Linux® is used pursuant to a sublicense from the Linux Foundation, the exclusive licensee of Linus Torvalds, owner of the mark on a worldwide basis.

LTO, Ultrium, the LTO Logo and the Ultrium logo are trademarks of HP, IBM Corp. and Quantum in the U.S. and other countries.

Red Hat, Ansible, OpenShift, are trademarks or registered trademarks of Red Hat, Inc. or its subsidiaries in the United States and other countries.

Other company, product, or service names may be trademarks or service marks of others.

### **Preface**

This IBM Redpaper publication provides a broad understanding of a new architecture of the IBM Power E1080 (also known as the Power E1080) server that supports IBM AIX®, IBM i, and selected distributions of Linux operating systems. The objective of this paper is to introduce the Power E1080, the most powerful and scalable server of the IBM Power portfolio, and its offerings and relevant functions:

- ▶ Designed to support up to four system nodes and up to 240 IBM Power10 processor cores The Power E1080 can be ordered as a 1-, 2-, 3-, or four-node configuration with each node providing up to 60 Power10 processor cores to a maximum 240 Power10 processor cores in a 4-node configuration.

- Designed to support up to 64 TB of memory

- The Power E1080 can be initially ordered with the total memory capacity of up to 8 TB. It supports up to 64 TB in a full combined four-system nodes server.

- Designed to support up to 32 Peripheral Component Interconnect Express (PCIe) Gen 5 slots in a full combined four-system nodes server, and up to 192 PCIe Gen 3 slots with expansion I/O drawers

- Up to over 4,000 directly attached serial-attached SCSI (SAS) disks or solid-state drives (SSDs)

- ▶ Up to 1,000 virtual machines (VMs) with logical partitions (LPARs) per system

- System control unit (SCU), providing redundant system master Flexible Service Processor (FSP)

- Supports IBM Power Private Cloud Solution with Dynamic Capacity

This publication is for professionals who want to acquire a better understanding of Power servers. The intended audience includes the following roles:

- Customers

- ► Sales and marketing professionals

- ► Technical support professionals

- ► IBM Business Partners

- Independent software vendors (ISVs)

This paper does not replace the current marketing materials and configuration tools. It is intended as an extra source of information that, together with existing sources, can be used to enhance your knowledge of IBM® server solutions.

#### **Authors**

This paper was produced by a team of specialists from around the world working at IBM Redbooks, Poughkeepsie Center.

**Tim Simon** is an IBM Redbooks® Project Leader who is based in Tulsa, Oklahoma, US. He has over 40 years of experience with IBM, primarily in a technical sales role working with customers to help them create IBM solutions to solve their business problems. He holds a BS degree in Math from Towson University in Maryland. He has worked with many IBM products and has extensive experience creating customer solutions by using IBM Power, IBM Storage, and IBM Z® throughout his career.

**Dean Mussari** is an IBM Power Brand Technical Specialist in the National Market in the US. He recently came to IBM, bringing 35 years of experience working with IBM servers and storage solutions in large retail environments. His main area of expertise is Power servers with a focus on IBM i. He holds a masters degree in computer science from Loyola University of Chicago.

**Tsvetomir Spasov** is a Power Servers Hardware Product Engineer in Sofia, Bulgaria. He has 8 years of experience with IBM in RTS, SME, and PE roles. His main area of expertise is Hardware Management Console (HMC), FSP, eBMC, POWERLC, and GTMS. He holds a masters degree in Electrical Engineering from Technical University of Sofia.

Thanks to the following people for their contributions to this project:

Thanks to the authors of the previous editions of this paper.

Authors of the first edition, *IBM Power E1080 Technical Overview and Introduction*, REDP-5649, published in October 2021, were:

Scott Vetter, Giuliano Anselmi, Manish Arora, Ivaylo Bozhinov, Dinil Das, Turgut Genc, Bartlomiej Grabowski, Madison Lee, Armin Röllr

#### Now you can become a published author, too!

Now you can become a published author, too!

Here's opportunity to spotlight your skills, grow your career, and become a published author—all at the same time! Join an IBM Redbooks residency project and help write a book in your area of expertise, while honing your experience using leading-edge technologies. Your efforts will help to increase product acceptance and customer satisfaction, as you expand your network of technical contacts and relationships. Residencies run from two to six weeks in length, and you can participate either in person or as a remote resident working from your home base.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

#### **Comments welcome**

Your comments are important to us!

We want our papers to be as helpful as possible. Send us your comments about this paper or other IBM Redbooks publications in one of the following ways:

▶ Use the online **Contact us** review Redbooks form found at:

ibm.com/redbooks

Send your comments in an email to:

redbooks@us.ibm.com

Mail your comments to:

IBM Corporation, IBM Redbooks Dept. HYTD Mail Station P099 2455 South Road Poughkeepsie, NY 12601-5400

# Stay connected to IBM Redbooks

► Find us on LinkedIn:

http://www.linkedin.com/groups?home=&gid=2130806

► Explore new Redbooks publications, residencies, and workshops with the IBM Redbooks weekly newsletter:

https://www.redbooks.ibm.com/Redbooks.nsf/subscribe?OpenForm

▶ Stay current on recent Redbooks publications with RSS Feeds:

http://www.redbooks.ibm.com/rss.html

# **Summary of changes**

This section describes the technical changes that were made in this edition of the paper and in previous editions. This edition might also include minor corrections and editorial changes that are not identified.

Summary of Changes for REDP-5649-01 IBM Power E1080 Technical Overview and Introduction as created or updated on November 15, 2024.

#### **November 2024, Second Edition**

This revision includes the following new and changed information.

#### **New information**

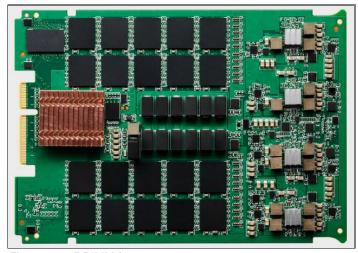

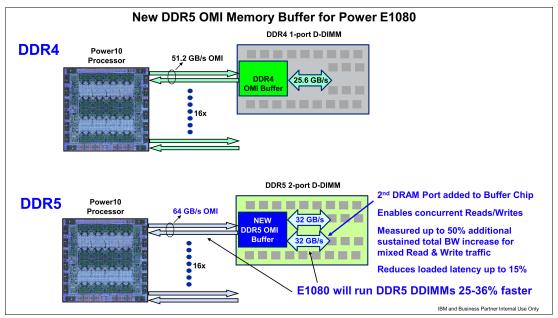

- ▶ Added information on Double Data Rate 5 (DDR5)-based differential dual inline memory modules (DDIMMs), which provide increased memory throughput and reduced latency compared to the Double Data Rate 4 (DDR4)-based memory that originally was delivered with IBM Power10.

- ▶ Added information about the Peripheral Component Interconnect Express (PCIe) Gen 4 Expansion drawer, which replaces the previous PCIe Gen 3 Expansion drawer. This expansion drawer can hold more PCIe adapters for your system, and provides improved throughput over the previous version.

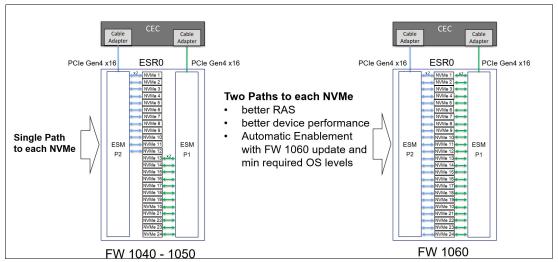

- ▶ Added information about the NED24 Non-Volatile Memory Express (NVMe) Expansion drawer. This new expansion drawer provides more NVMe slots for U2 NVMe devices. Each NED24 expansion drawer can provide up to 153 TB of capacity. Up to three NED24 drawers are supported per system node, providing up to 460 TB of capacity per drawer or over 1840 TB per system.

- ► This section also includes information about the multipath support in the NED24 expansion drawer.

- Added information about new adapters that are supported in the Power E1080.

#### **Changed information**

- ▶ Noted that the PCIe Gen 3 Expansion drawer is withdrawn from marketing. The replacement is the PCIe Gen 4 expansion drawer.

- ▶ Noted that the EXP24SX serial-attached SCSI (SAS) expansion drawer is withdrawn from marketing. The recommended replacement is the NED24 expansion drawer because it generally provides better performance and often lower costs compared to equivalent SAS storage options.

# 1

# **Introducing IBM Power E1080**

The Power E1080 is the newest addition to the IBM Power family, the industry's best-in-class server platform for security and reliability. The Power E1080 introduces the essential enterprise hybrid cloud platform, which is uniquely designed to help you securely and efficiently scale core operational and artificial intelligence (AI) applications anywhere in a hybrid cloud.

The Power E1080 simplifies end-to-end encryption and brings AI where your data is stored for faster insights. This configuration helps enable greater workload deployment flexibility and agility while accomplishing more work.

The Power E1080 can help you to realize the following benefits:

- ► Protect trust from core to cloud

- Protect data that is in-transit and at-rest with greatly simplified end-to-end encryption across hybrid cloud without affecting performance.

- Enjoy enterprise quality of service (QoS)

- The Power E1080 can detect, isolate, and recover from soft errors automatically in the hardware without taking an outage or relying on an operating system to manage the faults.

- ► Drive greater efficiency with sustainable and scalable compute

The processor performance, massive system throughput, and memory capacity qualify the Power E1080 server to be the perfect workload consolidation platform. This performance leads to significant savings in floor space, energy consumption, and operational expenditure costs.

This chapter includes the following topics:

- ► 1.1, "System overview" on page 2

- ► 1.2, "System nodes" on page 7

- ► 1.3. "System control unit" on page 10

- ► 1.4, "Server specifications" on page 12

- ▶ 1.5, "System features" on page 15

- ► 1.6, "I/O drawers" on page 25

- 1.7, "System racks" on page 30

- ▶ 1.8, "Hardware Management Console overview" on page 39

#### 1.1 System overview

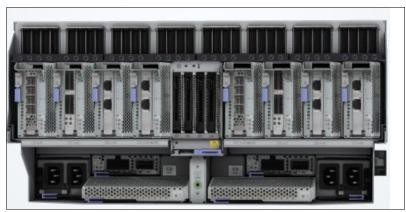

The Power E1080, also referred to by its 9080-HEX machine type-model designation, represents the most powerful and scalable server in the IBM Power portfolio. It is composed of a combination of central electronic complex (CEC) enclosures that are called *nodes* (or *system nodes*) and more units and drawers.

#### 1.1.1 System nodes, processors, and memory

In this section, we provide a general overview of the system nodes, processors, and memory. For more information about the system nodes, see 1.2, "System nodes" on page 7.

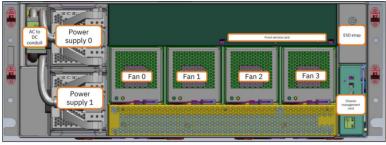

A *system node* is an enclosure that provides the connections and supporting electronics to connect the processor with the memory, internal disk, adapters, and the interconnects that are required for expansion. A combination of one, two, three, or four system nodes per server is supported.

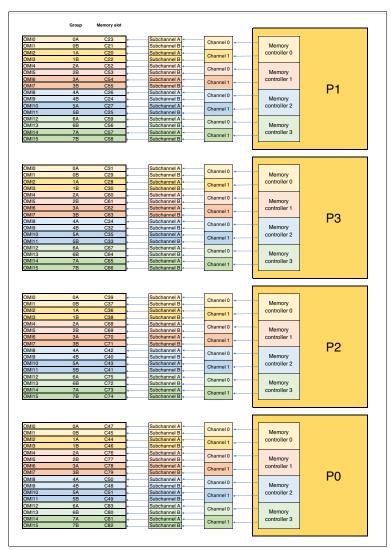

Each system node provides four sockets for Power10 processor chips and 64 differential dual inline memory module (DDIMM) slots for Double Data Rate 5 (DDR5) or Double Data Rate 4 (DDR4) technology DIMMs.

Each socket holds one Power10 single-chip module (SCM). An SCM can contain 10, 12, or 15 Power10 processor cores. It also holds the extra infrastructure logic to provide electric power and data connectivity to the Power10 processor chip.

A 4-node Power E1080 server scales up to 16 processor sockets and 160, 192, or 240 cores, depending on the number of cores that is provided by the configured SCM type.

The processor configuration of a system node is defined by the selected processor feature. Each feature defines a set of four Power10 processors chips with the same core density (10, 12, or 15). All system nodes within a Power E1080 server must be configured with the same processor feature.

Each system node can support up to a maximum of 16 TB of system memory by using the largest available memory DIMM. A fully configured 4-node Power E1080 can support up to 64 TB of memory.

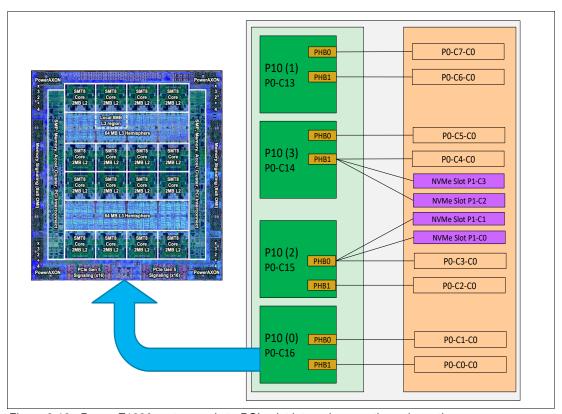

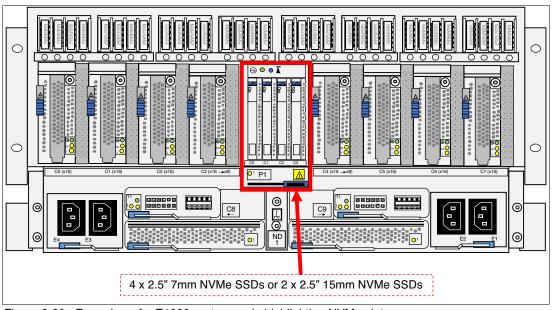

To provide internal boot capability, each system node enables up to four Non-Volatile Memory Express (NVMe) drive bays. More drive bays can be configured by using expansion drawers.

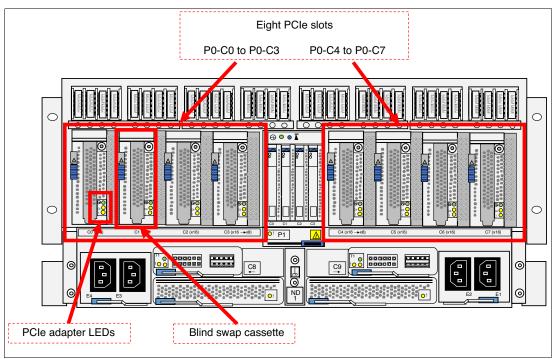

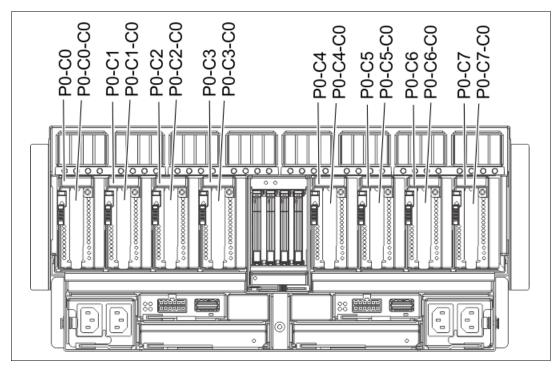

Each system node provides eight Peripheral Component Interconnect Express (PCIe) Gen 5 capable slots, with a maximum of 32 per Power E1080 server.

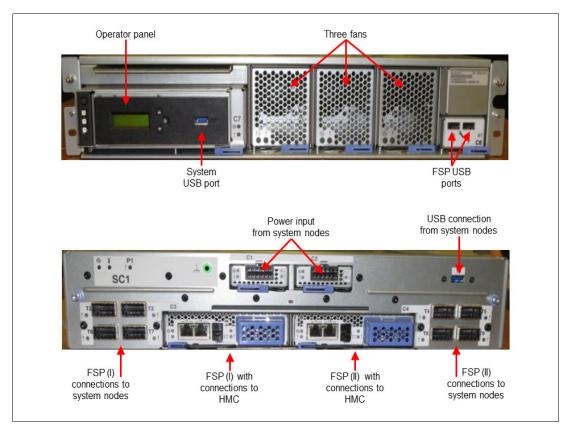

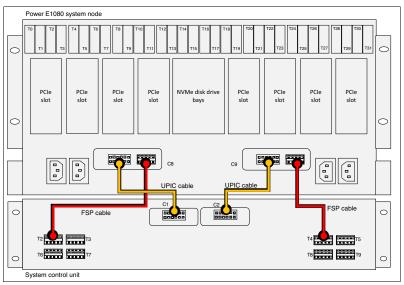

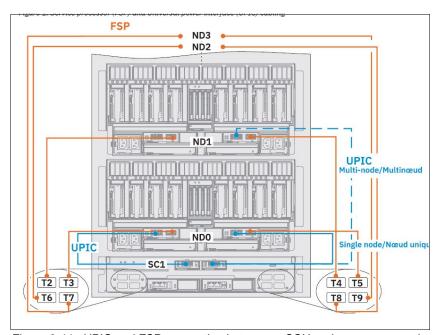

The system control unit (SCU) is required in all configurations. The SCU provides system hardware, firmware, and virtualization control through redundant Flexible Service Processors (FSPs). Only one SCU is required and supported for every Power E1080 server. For more information about the SCU, see 1.3, "System control unit" on page 10.

For more information about the environmental and physical aspects of the server, see 1.4, "Server specifications" on page 12.

#### 1.1.2 Expansion drawers and storage enclosures

More PCIe slots can be added by using expansion drawers, and more disk capacity can be added to your system by using storage enclosures.

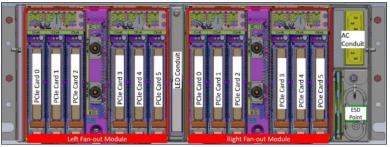

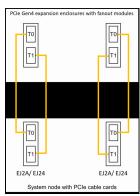

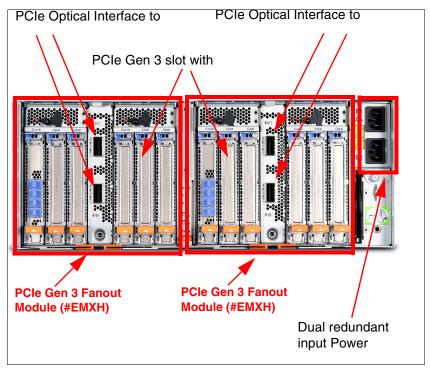

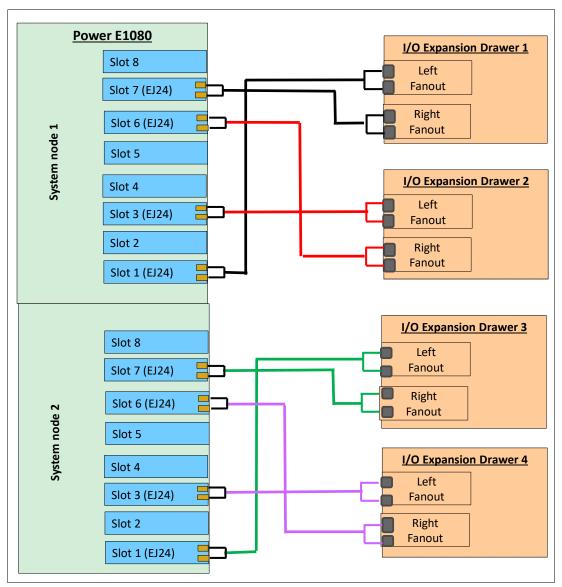

An expansion drawer provides more PCIe slots for I/O connectivity if needed. There are two versions of the PCIe expansion drawer: the original version supporting PCIe Gen 3 I/O slots<sup>1</sup>, and a newer version supporting PCIe Gen 4 I/O slots. There is no upgrade path from the Gen3 version to the Gen4 version, but you may mix the two I/O expansion drawers within a single system.

The I/O expansion drawer is a 19-inch PCIe 4U enclosure that provides up to 12 PCIe slots and connects to the system node with a pair of PCIe x16 to CXP converter cards (fanout adapters) that are housed in the system node. Each system node can support up to three Gen 4 I/O expansion drawers or four Gen 3 I/O expansion drawers, for a total of 48 PCIe Gen 3 slots or 36 PCIe Gen 4 slots. A fully configured Power E1080 can support a maximum of 16 Gen 3 I/O expansion drawers, providing a total of 192 PCIe Gen 3 slots or a maximum of 12 Gen 4 I.O expansion drawers for a total of 144 Gen 4 I/O slots.

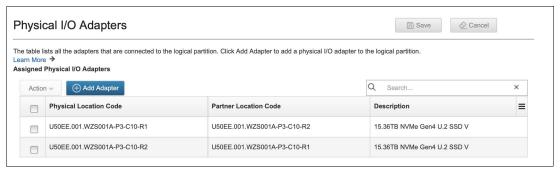

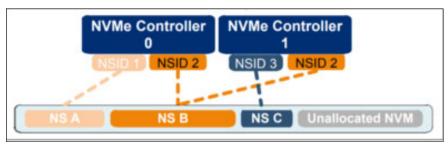

An optional NVMe expansion capability is provided by the NED24 NVMe expansion drawer. The NED24 attaches to the system units by using the same fanout adapters that are used by the I/O expansion drawers and provides up to 24 NVMe U2 drive slots. Each NVMe drive can be individually assigned to its own partition, providing great flexibility for boot images and more data for each partition.

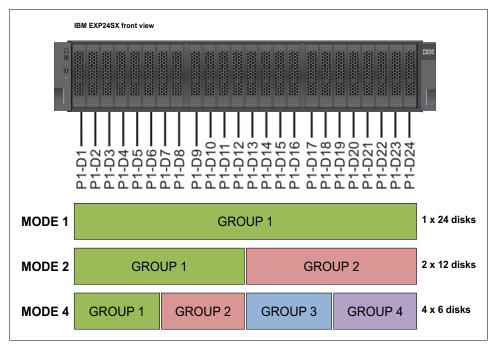

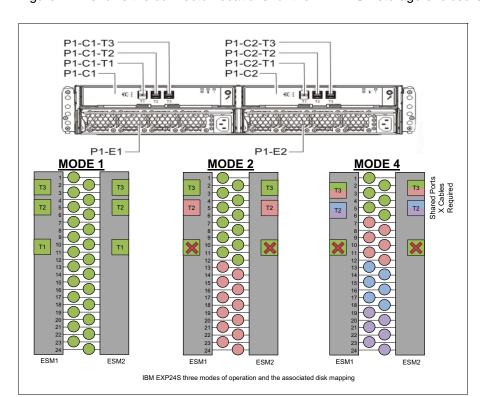

More serial-attached SCSI (SAS) storage can be implemented by using the EXP24SX SAS storage enclosure<sup>2</sup>, which provides twenty-four 2.5-inch small form factor (SFF) SAS bays. It supports up to 24 hot-swap hard disk drives (HDDs) or solid-state drives (SSDs) in only 2U rack units of space in a 19-inch rack. The EXP24SX is connected to the Power E1080 server by using SAS adapters that are plugged into PCIe slots either in the system nodes or in an I/O expansion drawer.

For more information about enclosures and drawers, see 1.6, "I/O drawers" on page 25.

More storage can also be allocated externally by using Storage Network Connections through the appropriate adapters that are installed in the system PCIe slots. For more information about IBM storage products, see this web page.

#### 1.1.3 Hardware at-a-glance

The Power E1080 server provides the following hardware components and characteristics:

- ▶ 10-, 12-, or 15-core Power10 processor chips that are packaged in an SCM per socket.

- One, two, three, or four system nodes with four Power10 processor sockets each.

- ► Redundant clocking in each system node.

- ▶ Up to 60 Power10 processor cores per system node and up to 240 per system.

- ▶ Up to 16 TB of memory per system node and up to 64 TB per system. Either DDR4 or DDR5 memory are supported.

- ► Eight PCle Gen 5 slots per system node and a maximum of 32 PCle Gen 5 slots per system.

<sup>&</sup>lt;sup>1</sup> The PCIe Gen 3 I/O drawer was withdrawn from marketing as of January 2024.

<sup>&</sup>lt;sup>2</sup> The EXP24SX was withdrawn from marketing, but is still supported.

- ► PCle Gen 1, Gen 2, Gen 3, Gen 4, and Gen 5 adapters are supported in the system nodes.

- ▶ Up to three PCle Gen 4 4U I/O expansion drawers per system node provide a maximum of 36 more PCle Gen 4 slots or up to four PCle Gen 3 expansion drawers for a maximum of 48 more PCle Gen 3 slots.

- ▶ Up to 144 PCIe Gen 4 slots that use 12 PCI Gen 4 expansion drawers or 192 PCIe Gen 3 slots that use 16 PCIe Gen 3 I/O expansion drawers per system.

- ▶ Up to over 4,000 directly attached SAS HDDs or SSDs through EXP24SX SFF drawers.

- Up to 288 directly attached external NVMe drives that use 12 NED24 NVMe expansion drawers.

- ► SCU, which provides redundant FSPs and support for the operations panel, the system vital product data (VPD), and externally attached DVD.

The massive computational power, exceptional system capacity, and the unprecedented scalability of the Power E1080 server hardware are provided by unique enterprise class firmware and system software capabilities and features. The following important characteristics and features are offered by the IBM Power enterprise platform:

- Support for IBM AIX, IBM i, and Linux operating system environments, including support for Red Hat OpenShift Cloud Platform.

- ► An innovative dense math engine (DME) that is integrated in each Power10 processor core to accelerate Al-inferencing workloads.

- Optimized encryption units that are implemented in each Power10 processor core.

- ► Dedicated data compression engines that are provided by the Power10 processor technology.

- ► Hardware- and firmware-assisted and enforced security provide trusted boot and pervasive memory encryption support.

- Up to 1,000 virtual machines (VMs) or logical partitions (LPARs) per system.

- Dynamic LPAR (DLPAR) support to modify available processor and memory resources according to workload, without interruption of the business.

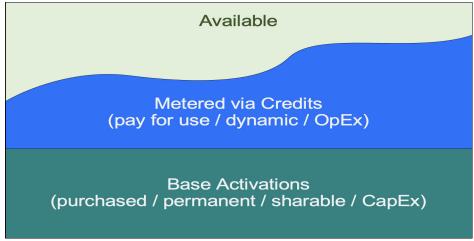

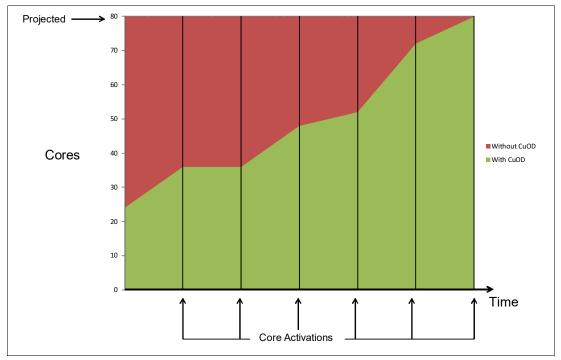

- ► Capacity on Demand (CoD) processor and memory options to help respond more rapidly and seamlessly to changing business requirements and growth.

- ▶ IBM Power Private Cloud Solution with Dynamic Capacity featuring Power Enterprise Pools 2.0 that supports unsurpassed enterprise flexibility for real-time workload balancing, system maintenance and operational expenditure cost management.

Table 1-1 compares important technical characteristics of the Power E1080 server with the Power E980 server, based on IBM Power9® processor-based technology.

| Table 1-1 | Comparing the Power E980 and the Power E1080 server |

|-----------|-----------------------------------------------------|

|-----------|-----------------------------------------------------|

| Features                     | Power E980 server              | Power E1080 server             |

|------------------------------|--------------------------------|--------------------------------|

| Processor                    | Power9                         | Power10                        |

| Processor package            | SCM                            | SCM                            |

| Cores per SCM                | 6, 8, 10, 11, 12               | 10, 12, 15                     |

| Number of cores per system   | Up to 192 cores                | Up to 240 cores                |

| Sockets per node             | 4                              | 4                              |

| System configuration options | 1-, 2-, 3-, and 4-node systems | 1-, 2-, 3-, and 4-node systems |

| Features                                            | Power E980 server                                                    | Power E1080 server                                                                                                            |

|-----------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Maximum memory per node                             | 16 TB                                                                | 16 TB                                                                                                                         |

| Maximum memory per system                           | 64 TB                                                                | 64 TB                                                                                                                         |

| Maximum memory bandwidth per node                   | 920 GBps                                                             | 1636 GBps                                                                                                                     |

| Aggregated maximum memory bandwidth per system      | 3680 GBps                                                            | 6544 GBps                                                                                                                     |

| Pervasive memory encryption                         | No                                                                   | Yes                                                                                                                           |

| PCle slots per node                                 | Eight PCIe Gen 4 slots                                               | Eight PCIe Gen 5 slots                                                                                                        |

| I/O drawer expansion option                         | Yes                                                                  | Yes                                                                                                                           |

| Acceleration ports                                  | Yes<br>CAPI 2.0 & OpenCAPI 3.0 <sup>a</sup>                          | Yes<br>OpenCAPI 3.0, 3.1                                                                                                      |

| PCle hot-plug Support                               | Yes                                                                  | Yes                                                                                                                           |

| I/O bandwidth per node                              | 545 GBps                                                             | 576 GBps                                                                                                                      |

| Integrated USB                                      | USB 3.0                                                              | Not available                                                                                                                 |

| Internal storage bays per node                      | Four NVMe PCIe Gen 3 bays <sup>b</sup>                               | Four NVMe PCle Gen 4 bays                                                                                                     |

| Per lane bit rate between sockets                   | 25 Gbps                                                              | 32 Gbps                                                                                                                       |

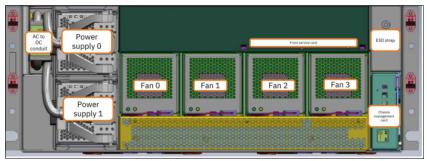

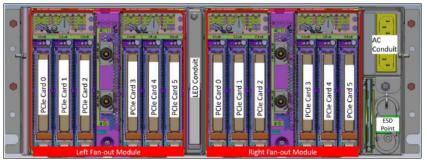

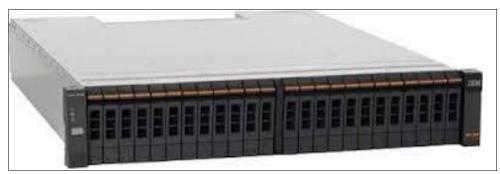

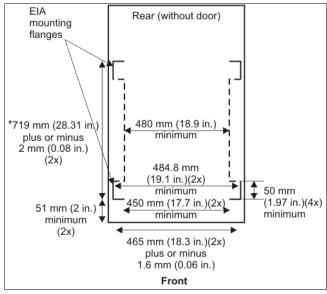

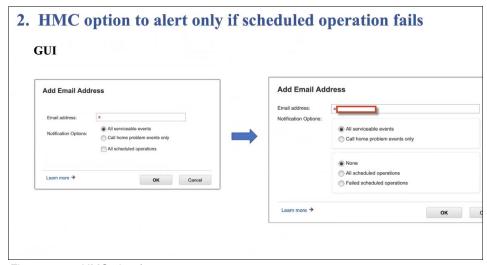

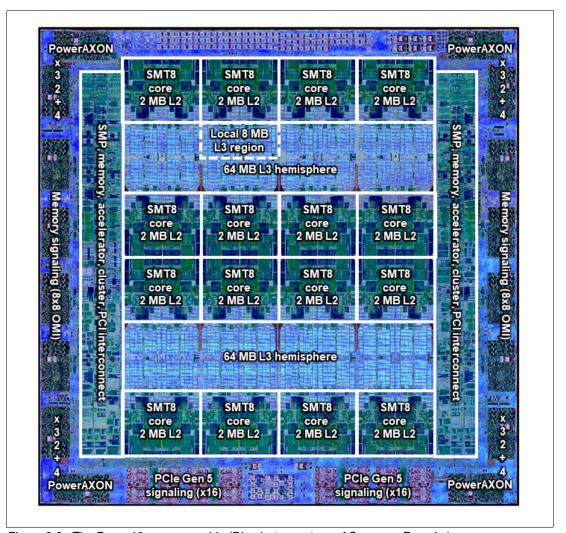

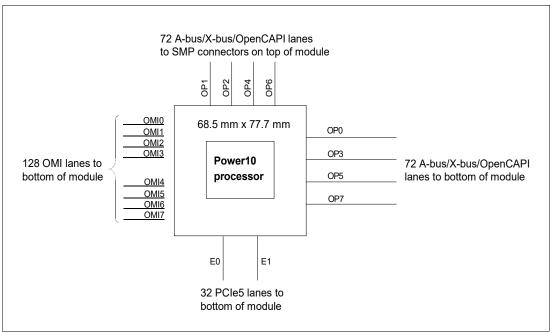

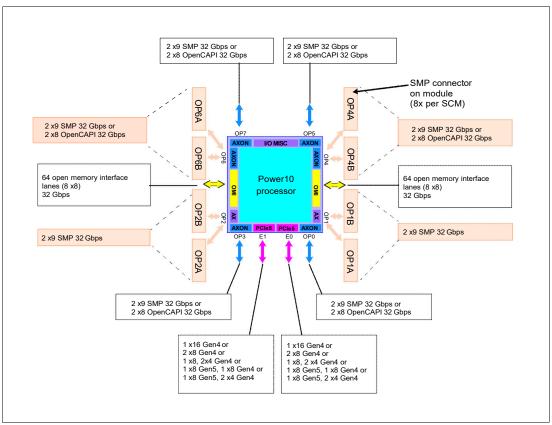

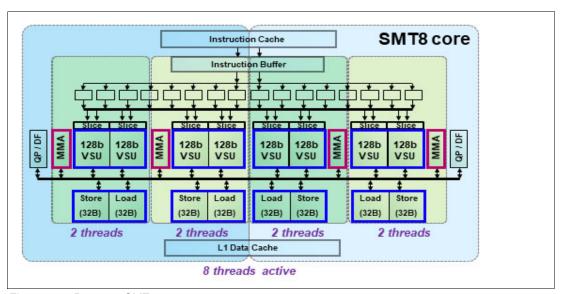

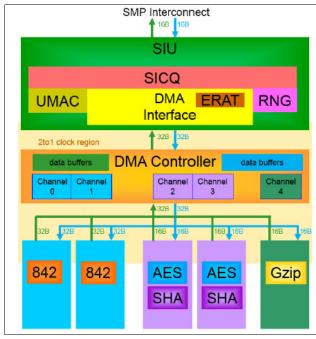

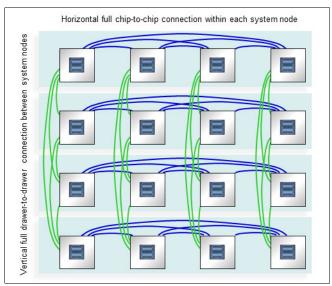

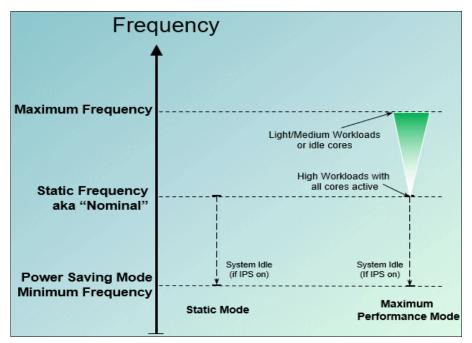

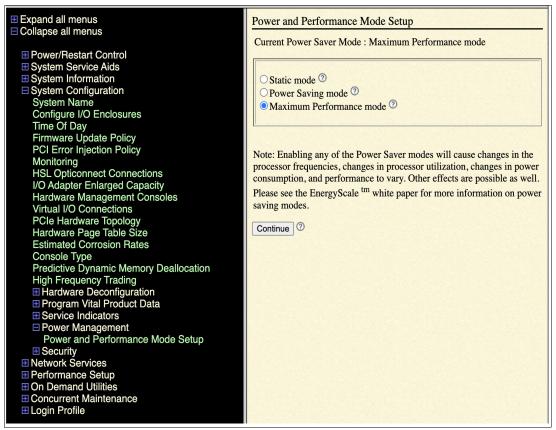

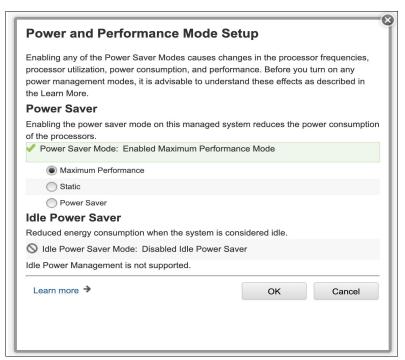

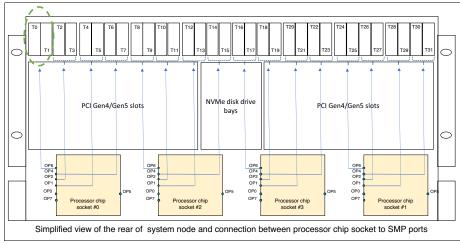

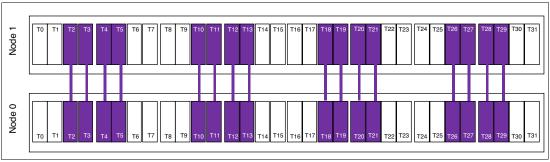

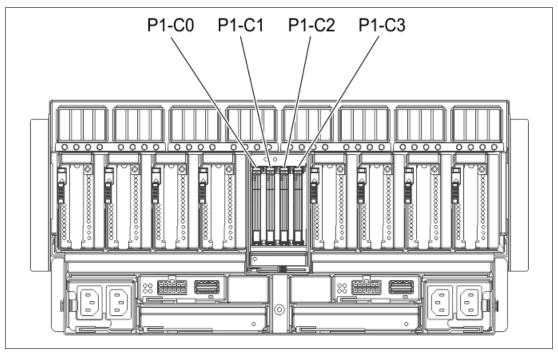

| Reliability, availability, and serviceability (RAS) | Symmetric multiprocessing (SMP) <sup>c</sup> cable concurrent repair | Non-active SMP cables with concurrent maintenance capability and time domain reflectometry (TDR) <sup>d</sup> fault isolation |